Xeon Phi

Ez a cikk a Xeon Phi-hez kapcsolódó különböző szempontokkal kíván foglalkozni, azzal a céllal, hogy az olvasó holisztikus képet adjon erről a témáról. Ezen a vonalon elemezzük a Xeon Phi jelentőségét különböző szférákban, valamint a mai társadalomra gyakorolt hatásait. Különböző nézőpontokat és megközelítéseket vizsgálunk meg, hogy teljes mértékben megértsük a Xeon Phi relevanciáját, valamint a kortárs világra gyakorolt hatását. Ezzel a cikkel az a cél, hogy olyan teljes áttekintést adjon, amely lehetővé teszi az olvasó számára, hogy elgondolkozzon és megalapozott véleményt alkosson a Xeon Phi-ről.

| Xeon Phi | |

| |

| Gyártás | 2010—2020[1] |

| Tervező | Intel |

| Max CPU órajel | 1,053 GHz – 1,7 GHz |

| Gyártás technológia méret | 22 nm (tri-gate), 14 nm (tri-gate) |

| Utasításkészlet | x86-64, kiterjesztések: AVX, AVX2, AVX-512 |

| Architektúra | x86-64 |

| Mikroarchitektúra | Larrabee, Airmont |

| Magok száma | 57-61 (x100 sorozat), 64-72 (x200 sorozat) |

| L1 gyorsítótár | 32 KiB magonként |

| L2 gyorsítótár | 512 KiB magonként |

| Foglalat | LGA 3647, PCIe 3.0 x16 |

| Alkalmazása | HPC, szuperszámítógépek |

| Utód | Sierra Forest |

A Wikimédia Commons tartalmaz Xeon Phi témájú médiaállományokat. | |

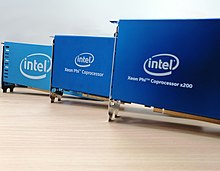

A Xeon Phi[2] egy az Intel által tervezett és gyártott x86 architektúrájú, nagymértékben párhuzamos, többmagos processzor-sorozat márkaneve. Szuperszámítógépekben, szerverekben és felső kategóriás munkaállomásokban való felhasználásra szánták. Architektúrája lehetővé tette a szabványos programozási nyelvek és alkalmazásprogramozási interfészek (API-k), például az OpenMP használatát.[3][4]

A Xeon Phi 2010-ben jelent meg. Mivel eredetileg az Intel egy korábbi GPU kialakításán (kódnevén "Larrabee") alapult,[5] amelyet 2009-ben töröltek,[6] ezért alkalmazási területei átfedésben voltak a grafikai processzorokéval (GPU-k). A legfőbb különbség a Xeon Phi és egy GPGPU között, mint pl. az Nvidia Tesla, az, hogy a Xeon Phi x86-kompatibilis magjaival kis módosítással olyan szoftvereket is futtathat, amelyeket eredetileg szabványos x86 CPU-ra szántak.

A második generációs Knights Landing kódnevű terméket 2013 júniusában jelentették be, ami PCIe-alapú bővítőkártyák formájában jelent meg.[7] Ezek a második generációs csipek önálló CPU-ként is használhatóak, nem csak egyszerű bővítőkártyaként.

2013 júniusában a kínai Kantoni Nemzeti Szuperszámítógépes Központ (NSCC-GZ) Tianhe-2 szuperszámítógépe volt a világ leggyorsabb szuperszámítógépe, az akkori bejelentés szerint.[8] Az elsőséget azóta elvesztette, 2018 júniusában a 4. helyen állt.[9] A Tianhe-2 Intel Xeon Phi koprocesszorokat és Ivy Bridge-EP Xeon processzorokat használt, amelyekkel 33,86 petaFLOPS teljesítményt ért el.[10]

A Xeon Phi termékvonal közvetlenül versengett az Nvidia Tesla és az AMD Radeon Instinct mélytanulási és GPGPU kártyák sorozataival. Megszűnt a kereslet hiánya és az Intel 10 nm-es gyártási folyamatának felfuttatásával kapcsolatos problémái miatt.[11] A cég 2018-ban megszüntette a x200-as Xeon Phi generációt, azaz a Knights Landing kódnevű lapkákra alapozott termékeket, majd 2019-ben a többi modellt is. A leadott rendeléseket 2020. július 31-ig teljesítették.

Történet

| Kódnév | Technológia | Megjegyzések |

|---|---|---|

| Knights Ferry | 45 nm | PCIe kártyaként kínálták; a Larrabee projektből származik |

| Knights Corner | 22 nm | a P54C-ből származik; vektoros feldolgozó egység; az első Xeon Phi-ként bejelentett eszköz |

| Knights Landing | 14 nm | a Silvermont / Airmont (Intel Atom) architektúrából származik;[12] AVX-512 |

| Knights Mill | 14 nm | majdnem azonos a Knights Landinggel, de mélytanulásra optimalizálva |

| Knights Hill | 10 nm | törölve |

Háttér

A Larrabee mikroarchitektúra (amelyet 2006 óta fejlesztenek[13]) nagyon széles (512 bites) SIMD egységeket vezetett be egy x86 architektúrán alapuló processzorkialakításba, és azt egy gyorsítótár-koherens multiprocesszoros rendszerré terjesztette ki, amely egy gyűrűs sínen (ring bus) keresztül kapcsolódik a memóriához, és minden egyes mag négyutas többszálas működésre képes. Mivel a terveket GPU-ban való felhasználás mellett általános célú számítási feladatokra is szánták, a Larrabee csipek textúra-mintavételezést szolgáló speciális hardvert is tartalmaznak.[14][15] A közvetlenül a Larrabee kutatási projektből kereskedelmi forgalomba hozható GPU termék elkészítését célzó projektet 2010 májusában leállították.[16]

Ezzel közel egy időben futott az Intel egy másik kutatási projektje, az „egycsipes felhő-számítógép” (Single-chip Cloud Computer) nevű, amely nem más, mint x86 architektúrájú processzorokkal felépített sokmagos processzortömb megvalósítása, egy egyetlen csipen felépített felhő alapú számítógépes adatközpontot utánzó felépítés, független magok sokaságával. Prototípusát 2009-ben mutatták be,[17] a prototípus terv 48 magot tartalmazott csipenként, hardveres támogatással a magok szelektív frekvencia- és feszültségszabályozásához az energiahatékonyság maximalizálása érdekében, és magában foglalt egy szövevényes hálózatot a csipek közötti üzenetátvitel céljára. A kialakításban nem szerepelnek gyorsítótár-koherens magok és azokra az elvekre fókuszál, amik lehetővé teszik a kialakítás kiterjesztését sokkal több mag használatára (skálázhatóság).[18]

A Teraflops kutatási csip az Intel egy kísérleti 80 magos csipje, prototípusát 2007. február 11-én mutatták be.[19] A csipen nem x86 architektúrájú magok találhatók, hanem egy 96 bites VLIW architektúrát implementáltak.[20] A magok mindegyike két lebegőpontos egységet, valamint egy routert tartalmaz a magok közötti kommunikációhoz. A projekt a magok közötti kommunikációs módszereket és a csipenkénti energiagazdálkodást vizsgálta, és elérte az 1,01 teraFLOPS sebességet, 3,16 GHz-es órajel és 62 W energiafelhasználás mellett.[21][22]

Knights Ferry

Az Intel a MIC (Many Integrated Core) tervezet keretén belül 2010. május 31-én mutatta be a Knights Ferry nevű, Aubrey Isle kódnevű processzort tartalmazó prototípus-kártyát. A kártyát illetve a későbbi termékcsaládot a cég kifejezetten HPC[23] alkalmazások futtatására tervezte. A termék a cég állításai szerint, és felépítését tekintve is a Larrabee tervezet egy származéka, de létrejöttében nagy szerepet játszottak az Intel egyéb kutatásai, főleg az „egycsipes felhő-számítógép” projekt eredményei.[24][25]

A fejlesztés eredményét PCIe kártya formájában hozták forgalomba. Benne 32 sorrendi végrehajtású mag található, a magok legfeljebb négy végrehajtási szálat képesek futtatni, órajelük 1,2 GHz, 2 GiB GDDR5 memóriával a kártyán,[26] összesen 8 MiB koherens megosztott L2-es gyorsítótárral: az L2 gyorsítótárat a magok közösen használják, ebből mindegyik maghoz 256 KiB-os szegmens tartozik, a magok emellett saját 32 KiB-os L1 gyorsítótárral rendelkeznek. A magokban egy skaláris egység és egy 512 bites vektoros egység található, amely 16 egyszeres pontosságú, vagy 8 kétszeres pontosságú műveletet végezhet.[26] A kártyán lévő csip 45 nm-es folyamattal készült,[27] energiaigénye közelítőleg 300 W.[26] Az Aubrey Isle magban a processzorok egy 1024 bites (két irányban 512 bites) gyűrűs sínnel csatlakoznak a főmemóriához.[28] Egy kártya teljesítménye meghaladja a 750 GFLOPS-ot.[27] A prototípus-kártyák csak az egyszeres pontosságú lebegőpontos utasításokat támogatják.[29]

A kezdeti fejlesztők között található a CERN, a koreai Korea Institute of Science and Technology Information (KISTI) és a németországi Garchingban található Leibniz Szuperszámítógép Központ. A prototípus-kártyákat alkalmazó hardvert (kiszolgálókat) IBM, SGI, HP, Dell és más cégek mutattak be.[30]

Knights Corner

A Knights Corner termékvonal 22 nm-es folyamatmérettel készült, az Intel Tri-gate tranzisztor-technológiáját alkalmazva.[31] Csipenként 50-nél több magot tartalmazhat, és ez az Intel első sokmagos terméke, ami kereskedelmi forgalomba került.[24][27]

2011 júniusában az SGI bejelentette, hogy együttműködik az Intellel a MIC architektúra alkalmazása terén nagy teljesítményű számítástechnikai termékeiben.[32] 2011 szeptemberében bejelentették, hogy a Texas Advanced Computing Center (TACC) Knights Corner kártyákat fog használni a 10-petaFLOPS teljesítményű „Stampede” szuperszámítógépében, ezzel biztosítva 8 petaFLOPS számítási teljesítményt.[33] Az idézett IEEE cikk szerint („Stampede: A Comprehensive Petascale Computing Environment”) „ második generációs Intel (Knights Landing) MIC csipeket adnak hozzá, amint azok elérhetővé válnak, és ezzel a Stampede összesített csúcsteljesítményét legalább 15 petaFLOPS-ra növelik.”[34][35]

2011. november 15-én az Intel bemutatta a Knights Corner processzor egy korai mikrocsipes változatát.[36][37]

2012. június 5-én az Intel a Knights Corner processzorra vonatkozó nyílt forráskódú szoftvert és dokumentációt adott ki.[38]

2012. június 18-án az Intel a 2012-es hamburgi nemzetközi szuperszámítógépes konferencián (International Supercomputing Conference, újabban: ISC High Performance) bejelentette, hogy az összes Intel MIC (Many Integrated Core) architektúrán alapuló termék márkaneve Xeon Phi lesz.[2][39][40][41][42][43][44] 2012 júniusában a Cray bejelentette, hogy felveszi kínálatába a 22 nm-es „Knights Corner” csipeket („Xeon Phi” márkanéven), a „Cascade” rendszerekben felhasználható társprocesszorként.[45][46]

2012 júniusában a ScaleMP bejelentett egy virtualizációs frissítést, amely lehetővé tette a Xeon Phi transzparens processzor-kiterjesztésként való használatát, így lehetővé téve régebbi/örökölt MMX/SSE kódok változtatás nélküli futtatását.[47] Az Intel Xeon Phi koprocesszor-magok egyik fontos összetevője a bennük lévő vektoros feldolgozó egység (VPU).[48] A VPU egy újszerű 512 bites SIMD utasításkészlet tartalmaz, amely hivatalosan az „Intel Initial Many Core Instructions” (kb. Intel Kezdő Sokmagos Utasítások, röviden Intel IMCI) néven ismert. Így a VPU ciklusonként 16 egyszeres pontosságú (SP) vagy 8 kétszeres pontosságú (DP) műveletet képes végrehajtani. A VPU támogatja az összevont szorzás-összeadás (FMA) utasításokat is, ezáltal ciklusonként 32 SP vagy 16 DP lebegőpontos művelet végrehajtására is képes. A VPU támogatja az egész számokat is. A VPU tartalmaz még egy kiterjesztett matematikai egységet is (EMU), amely olyan műveletek végrehajtására képes, mint a reciprok, négyzetgyök és logaritmus, lehetővé téve ezáltal e műveletek nagy sávszélességgel, vektoros módon történő végrehajtását. Az EMU a fenti függvényeket polinomiális közelítéssel számítja.

2012. november 12-én, az Intel két Xeon Phi koprocesszorcsaládot jelentett be, amelyek 22 nm-es gyártási folyamattal készülnek, a Xeon Phi 3100 és a Xeon Phi 5110P jelölésűeket.[49][50][51] A Xeon Phi 3100 több mint 1 teraFLOPS kétszeres pontosságú lebegőpontos utasítás végrehajtásra képes 240 GiB/s memória-sávszélességgel, 300 W fogyasztás mellett.[49][50][51] A Xeon Phi 5110P 1,01 teraFLOPS kétszeres pontosságú lebegőpontos utasítás végrehajtásra képes 320 GiB/s memória-sávszélességgel, 225 W fogyasztás mellett.[49][50][51] A Xeon Phi 7120P 1,2 teraFLOPS kétszeres pontosságú lebegőpontos utasítás végrehajtásra képes 352 GiB/s memória-sávszélességgel, 300 W-os fogyasztás mellett.

2013. június 17-én a Tianhe-2 szuperszámítógép a világ akkori leggyorsabbjaként a TOP500 listán megszerezte az első helyezést.[8] A Tianhe-2 az Intel Ivy Bridge Xeon és Xeon Phi processzorokat használva elérte a 33,86 petaFLOPS (lebegőpontos számítási) teljesítményt. Két és fél éven át ez volt a lista leggyorsabb számítógépe, utoljára 2015 novemberében.[52]

Felépítés és programozás

A Knights Corner magjai az eredeti Pentiumban használt P54C kialakítás módosított változatán alapulnak.[53] Az Intel MIC architektúra alapja az x86-os örökség kihasználása egy olyan x86-kompatibilis multiprocesszoros architektúra létrehozásával, ami képes a meglévő párhuzamosítási szoftvereszközök használatára.[27] A programozási eszközök között megtalálható az OpenMP,[54] OpenCL,[29] Cilk/Cilk Plus, az Intel Fortran, C++[55] és matematikai könyvtárak speciális változatai.[56]

A Larrabee projektből örökölt tervezési elemek közé tartozik a x86 ISA, a magonkénti 4 utas szimultán többszálas végrehajtás (simultaneous multithreading, SMT), az 512 bites SIMD egységek, a 32 KiB L1 utasítás-gyorsítótár, a 32 KiB L1 adat-gyorsítótár, a koherens L2 gyorsítótár (magonként 512 KiB[57]), valamint a processzorokat és a memóriát összekötő ultraszéles gyűrűs sín.

A Knights Corner 512 bites SIMD utasításai számos belső funkciót osztanak meg az AVX-512 kiterjesztéssel. Az utasításkészlet dokumentációja az Inteltől a KNC név-kiterjesztés alatt érhető el.[58][59][60][61]

- A Xeon Phi X100 sorozat modelljei

| név | kódszám | magok (szálak 4 magnál) |

órajel (MHz) | L2 gyorsítótár |

GDDR5 ECC memória | csúcs dp[62] teljesítmény (GFLOPS) |

TDP (W) |

hűtő- rendszer | kiszerelés | kibocsátva | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| alap | turbo | méret | csatornák | BW GiB/s | |||||||||

| Xeon Phi 3110X[63] | SE3110X | 61 (244) | 1053 | - | 30,5 MiB | 6 GiB | 12 | 240 | 1028 | 300 | csak kártya | PCIe 2.0 x16 kártya | 2012. november |

| 8 GiB | 16 | 320 | |||||||||||

| Xeon Phi 3120A[64] | SC3120A | 57 (228) | 1100 | - | 28,5 MiB | 6 GiB | 12 | 240 | 1003 | 300 | ventilátor / hűtőtest | 2013. június 17. | |

| Xeon Phi 3120P[65] | SC3120P | 57 (228) | 1100 | - | 28,5 MiB | 6 GiB | 12 | 240 | 1003 | 300 | passzív hűtőborda | 2013. június 17. | |

| Xeon Phi 31S1P[66] | BC31S1P | 57 (228) | 1100 | - | 28,5 MiB | 8 GiB | 16 | 320 | 1003 | 270 | passzív hűtőborda | 2013. június 17. | |

| Xeon Phi 5110P[67] | SC5110P | 60 (240) | 1053 | - | 30,0 MiB | 8 GiB | 16 | 320 | 1011 | 225 | passzív hűtőborda | 2012. november 12. | |

| Xeon Phi 5120D[68] | SC5120D | 60 (240) | 1053 | - | 30,0 MiB | 8 GiB | 16 | 352 | 1011 | 245 | csak kártya | SFF 230 tűs kártya | 2013. június 17. |

| BC5120D | |||||||||||||

| Xeon Phi SE10P[69] | SE10P | 61 (244) | 1100 | - | 30,5 MiB | 8 GiB | 16 | 352 | 1074 | 300 | passzív hűtőborda | PCIe 2.0 x16 kártya | 2012. november 12. |

| Xeon Phi SE10X[70] | SE10X | 61 (244) | 1100 | - | 30,5 MiB | 8 GiB | 16 | 352 | 1074 | 300 | csak kártya | 2012. november 12. | |

| Xeon Phi 7110P[71] | SC7110P | 61 (244) | 1100 | 1250 | 30.5 MiB | 16 GiB | 16 | 352 | 1220 | 300 | passzív hűtőborda | ??? | |

| Xeon Phi 7110X[72] | SC7110X | 61 (244) | 1250 | ??? | 30,5 MiB | 16 GiB | 16 | 352 | 1220 | 300 | csak kártya | ??? | |

| Xeon Phi 7120A[73] | SC7120A | 61 (244) | 1238 | 1333 | 30,5 MiB | 16 GiB | 16 | 352 | 1208 | 300 | ventilátor / hűtőtest | 2014. április 6. | |

| Xeon Phi 7120D[74] | SC7120D | 61 (244) | 1238 | 1333 | 30,5 MiB | 16 GiB | 16 | 352 | 1208 | 270 | csak kártya | SFF 230 tűs kártya | 2014. március ??. |

| Xeon Phi 7120P[75] | SC7120P | 61 (244) | 1238 | 1333 | 30,5 MiB | 16 GiB | 16 | 352 | 1208 | 300 | passzív hűtőborda | PCIe 2.0 x16 kártya | 2013. június 17. |

| Xeon Phi 7120X[76] | SC7120X | 61 (244) | 1238 | 1333 | 30,5 MiB | 16 GiB | 16 | 352 | 1208 | 300 | csak kártya | 2013. június 17. | |

Knights Landing

Az Intel második generációs MIC architektúrájú termékének kódneve.[34] 2013. június 17-én az Intel hivatalosan először mutatta be a második generációs Intel Xeon Phi termékek részleteit.[10] 2013. június 17-én az Intel közölte, hogy az Intel MIC architektúrán alapuló termékek következő generációja kétféle formában lesz elérhető, koprocesszorként és fő processzorként (CPU), és az Intel 14 nm-es gyártástechnológiájával készülnek. A Knights Landing termékek integrált, egységen belüli memóriát tartalmaznak majd a jelentősen nagyobb memória sávszélesség elérése érdekében.

A Knights Landing max. 72 Airmont (Atom) magot tartalmaz, magonként négy végrehajtási szállal,[77][78] LGA 3647 foglalatot használ[79] és akár 384 GiB „távoli” DDR4 2133 RAM-ot és 8–16 GiB egymásra épített (stacked) „közeli” 3D MCDRAM-ot (a Hybrid Memory Cube egy változata) támogat. Minden mag két 512 bites vektoregységgel rendelkezik, és támogatja az AVX-512 SIMD utasításokat, specifikusan az Intel AVX-512 Foundational Instructions (alapvető utasítások, AVX-512F), Intel AVX-512 Conflict Detection Instructions (konfliktusészlelő utasítások, AVX-512CD), Intel AVX-512 Exponential and Reciprocal Instructions (exponenciális és reciprok utasítások, AVX-512ER), és Intel AVX-512 Prefetch Instructions (előzetes utasításkód-lehívó utasítások, AVX-512PF) utasítás-csoportokat. Az IMCI támogatása megszűnt, ezt váltotta fel az AVX-512.[80]

A National Energy Research Scientific Computing Center (2018-ban?) bejelentette, hogy a legújabb „Cori” nevű szuperszámítógépének második fázisa Knights Landing Xeon Phi koprocesszorokat fog használni.[81]

2016. június 20-án az Intel bemutatta a Knights Landing architektúrán alapuló x200 sorozatú Intel Xeon Phi termékcsaládot, hangsúlyozva annak alkalmazhatóságát nemcsak a hagyományos szimulációs feladatokra, hanem a gépi tanulásban is.[82][83] A bemutatkozó modellkészletben csak bootolható kiszerelésű (önálló processzorként működő) Xeon Phi modellek szerepeltek, de annak két változata: szabványos processzorok és integrált Intel Omni-Path architektúrájú szövedéket (fabric) tartalmazó processzorok.[84] Ez utóbbit a modellszám F utótagja jelöli. Az integrált szerkezettől azt várják, hogy jobb késleltetési időt biztosít alacsonyabb költséggel, mint a diszkrét nagy teljesítményű hálózati kártyák.[82]

2016. november 14-én, a TOP500 48-ik listáján[85] 10 Knights Landing platformot használó rendszer szerepelt.

A Knights Landing PCIe-alapú társprocesszoros változata nem került forgalomba, és megszűnt 2017 augusztusában.[86] Ez magában foglalta a 7220A, 7240P és 7220P társprocesszor-kártyákat.

Az Intel bejelentette, hogy 2018 nyarán megszünteti a Knights Landinget.[87]

- Modellek

Minden modell képes megnövelni a sebességét, 200 MHz-cel növelve az alapfrekvenciát, mikor csak egy vagy két magot használ. Háromtól a maximális magok számáig a lapkák csak 100 MHz-cel tudják növelni az alapfrekvenciát. Minden csip a sűrű (optimizált) AVX[88] kódot 200 MHz-cel csökkentett frekvencián futtatja.[89]

| Xeon Phi 7200 sorozat | sSpec szám | magok (szálak) | órajel (MHz) | L2 gyorsítótár |

MCDRAM memória | DDR4 memória | csúcs dp[62] teljesítmény | TDP (W) |

foglalat | kiadás | azonosító | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| alap | turbo | méret | BW | méret | BW | |||||||||

| Xeon Phi 7210[90] | SR2ME (B0) | 64 (256) | 1300 | 1500 | 32 MiB | 16 GiB | 400+ GiB/s | 384 GiB | 102,4 GiB/s | 2662 GFLOPS |

215 | SVLCLGA3647 | 2016. június 20. | HJ8066702859300 |

| SR2X4 (B0) | ||||||||||||||

| Xeon Phi 7210F[91] | SR2X5 (B0) | 230 | HJ8066702975000 | |||||||||||

| Xeon Phi 7230[92] | SR2MF (B0) | 215 | HJ8066702859400 | |||||||||||

| SR2X3 (B0) | ||||||||||||||

| Xeon Phi 7230F[93] | SR2X2 (B0) | 230 | HJ8066702269002 | |||||||||||

| Xeon Phi 7250[94] | SR2MD (B0) | 68 (272) | 1400 | 1600 | 34 MiB | 3046 GFLOPS[95] |

215 | HJ8066702859200 | ||||||

| SR2X1 (B0) | ||||||||||||||

| Xeon Phi 7250F[96] | SR2X0 (B0) | 230 | HJ8066702268900 | |||||||||||

| Xeon Phi 7290[97] | SR2WY (B0) | 72 (288) | 1500 | 1700 | 36 MiB | 3456 GFLOPS |

245 | HJ8066702974700 | ||||||

| Xeon Phi 7290F[98] | SR2WZ (B0) | 260 | HJ8066702975200 | |||||||||||

Knights Hill

A Knights Hill volt a MIC architektúra harmadik generációjának kódneve, amelyről az Intel az első részleteket a 2014-es „SC14” Szuperszámítógépes Konferencián (New Orleans, LA, 2014. nov. 16-17.) jelentette be.[99] 10 nm-es eljárással tervezték gyártani.[100]

A Knights Hill-t várhatóan az Egyesült Államok Energiaügyi Minisztériuma Aurora szuperszámítógépében tervezték alkalmazni, amelyet az Argonne Nemzeti Laboratóiumban telepítettek volna.[101][102] Azonban az Aurora megjelenése késett a „fejlett architektúra” bevezetése miatt, amely a gépi tanulást célozta.[103][104]

2017-ben az Intel bejelentette, hogy a Knights Hill-t törölték egy másik architektúra javára, amelyet az alapoktól kezdve építenek fel, hogy a jövőben lehetővé tegye az exascale számításttechnikát. Ez az új architektúra 2020–2021-ben volt várható.[105][106]

Knights Mill

A Knights Mill az Intel kódneve egy „mélytanulásra” specializált Xeon Phi terméknek,[107] amelyet eredetileg 2017 decemberében adtak ki.[108] A Knights Landinggel szinte azonos specifikációkkal rendelkező Knights Mill az AVX-512 utasítások jobb kihasználását célzó optimalizálásokat tartalmaz és lehetővé teszi a négyutas hyper-threadinget. Az egyszeres pontosságú és változó pontosságú lebegőpontos teljesítmény megnövekedett, a kétszeres pontosságú lebegőpontos teljesítmény rovására.

- Modellek

| Xeon Phi 72x5 sor |

sSpec szám | magok (szálak) | órajel (MHz) | L2 gyorsítótár |

MCDRAM memória | DDR4 memória | csúcs dp[62] teljesítmény | TDP (W) |

foglalat | kiadás | azonosító | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| alap | turbo | méret | BW | méret | BW | |||||||||

| Xeon Phi 7235 | SR3VF (A0) | 64 (256) | 1300 | 1400 | 32 MiB | 16 GiB | 400+ GiB/s | 384 GiB | 102,4 GiB/s | ? | 250 | SVLCLGA3647 | Q4 2017 | HJ8068303823900 |

| Xeon Phi 7285 | SR3VE (A0) | 68 (272) | 1300 | 1400 | 34 MiB | 115,2 GiB/s | ? | 250 | HJ8068303823800 | |||||

| Xeon Phi 7295 | SR3VD (A0) | 72 (288) | 1500 | 1600 | 36 MiB | 115,2 GiB/s | ? | 320 | HJ8068303823700 | |||||

Programozás

A kutatók empirikus teljesítmény- és programozhatósági vizsgálatot végeztek,[109] amelyben a szerzők azt állítják, hogy a Xeon Phi nagy teljesítményének kihasználásához (eléréséhez) továbbra is szükség van a programozók segítségére, és hogy csupán a hagyományos programozási modelleket alkalmazó fordítóprogramokra támaszkodva optimális programkódot előállítani még mindig messze van a valóságtól. Ugyanakkor különböző területeken, mint például az élettudományok,[110] és mélytanulás[111] területén végzett kutatások kimutatták, hogy a Xeon Phi szál- és SIMD-párhuzamosságát együttesen kihasználva jelentős sebességnövekedés érhető el.

Konkurencia

- Nvidia Tesla – egy közvetlen versenytársa a HPC-piacon[112]

- AMD Radeon Pro és AMD Radeon Instinct – szintén közvetlen versenytársak a HPC piacon

Jegyzetek

- ↑ Ian Cutress & Anton Shilov: The Larrabee Chapter Closes: Intel's Final Xeon Phi Processors Now in EOL, 2019. május 7. (Hozzáférés: 2020. március 12.)

- ↑ a b Radek. „Chip Shot: Intel Names the Technology to Revolutionize the Future of HPC - Intel Xeon Phi Product Family”, Intel, 2012. június 18. (Hozzáférés: 2012. december 12.)

- ↑ robert-reed: Best Known Methods for Using OpenMP on Intel Many Integrated Core (Intel MIC) Architecture. software.intel.com , 2013. február 4.

- ↑ Intel Xeon Phi Coprocessor High Performance Programming. Morgan Kaufmann (2013. március 1.). ISBN 978-0124104143

- ↑ Hruska, Joel: Intel Quietly Kills Off Xeon Phi. ExtremeTech , 2019. május 8.

- ↑ Intel scraps graphics chip based on Larrabee. Reuters, 2009. december 6.

- ↑ (2016) „Knights Landing: Second-Generation Intel Xeon Phi Product”. IEEE Micro 36 (2), 34–46. o. DOI:10.1109/MM.2016.25.

- ↑ a b TOP500 - June 2013. TOP500. (Hozzáférés: 2013. június 18.)

- ↑ June 2018 /!/ TOP500 Supercomputer Sites (angol nyelven). www.top500.org . (Hozzáférés: 2018. július 22.)

- ↑ a b Intel Powers the World's Fastest Supercomputer, Reveals New and Future High Performance Computing Technologies. (Hozzáférés: 2013. június 21.)

- ↑ W1zzard: Intel is Giving up on Xeon Phi - Eight More Models Declared End-Of-Life. TechPowerUp , 2018. július 24.

- ↑ Marc Sauter: Knights Landing: Intel veröffentlicht Xeon Phi mit bis zu 7 Teraflops - Golem.de (német nyelven). www.golem.de , 2016. június 20.

- ↑ Charlie Demerjian (3 July 2006), New from Intel: It's Mini-Cores!, The Inquirer, <https://www.theinquirer.net/inquirer/news/1029138/new-from-intel-its-mini-cores> Archiválva 2009. augusztus 29-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ (2008. augusztus 1.) „Larrabee: A Many-Core x86 Architecture for Visual Computing”. ACM Transactions on Graphics 27 (3), 18:11. o. . DOI:10.1145/1360612.1360617. ISSN 0730-0301. (Hozzáférés: 2022. augusztus 5.)

- ↑ Tom Forsyth, SIMD Programming with Larrabee, Intel, <https://www.stanford.edu/class/ee380/Abstracts/100106-slides.pdf>

- ↑ Ryan Smith (25 May 2010), Intel Kills Larrabee GPU, Will Not Bring a Discrete Graphics Product to Market\, AnandTech, <https://www.anandtech.com/show/3738/intel-kills-larrabee-gpu-will-not-bring-a-discrete-graphics-product-to-market>

- ↑ Tony Bradley (3 December 2009), Intel 48-Core "Single-Chip Cloud Computer" Improves Power Efficiency, PCWorld, <https://www.pcworld.com/article/183653/intel_48core_singlechip_cloud_computer_improves_power_efficiency.html>

- ↑ Intel Research : Single-Chip Cloud Computer, Intel, <http://techresearch.intel.com/ProjectDetails.aspx?Id=1>

- ↑ Ben Ames (11 February 2007), Intel Tests Chip Design With 80-Core Processor, IDG News, <https://www.pcworld.com/article/128924/intel_tests_chip_design_with_80core_processor.html> Archiválva 2012. január 17-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ Intel Details 80-Core Teraflops Research Chip - X-bit labs. xbitlabs.com. . (Hozzáférés: 2015. augusztus 27.)

- ↑ Intel's Teraflops Research Chip, Intel, <https://download.intel.com/pressroom/kits/Teraflops/Teraflops_Research_Chip_Overview.pdf>

- ↑ Anton Shilov (12 February 2007), Intel Details 80-Core Teraflops Research Chip, Xbit laboratories, <http://www.xbitlabs.com/news/cpu/display/20070212224710.html> Archiválva 2015. február 5-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ high performance computing, nagy teljesítményű számítástechnika

- ↑ a b Rupert Goodwins (1 June 2010), Intel unveils many-core Knights platform for HPC, ZDNet, <http://www.zdnet.co.uk/news/desktop-hardware/2010/06/01/intel-unveils-many-core-knights-platform-for-hpc-40089093/>

- ↑ Intel News Release : Intel Unveils New Product Plans for High-Performance Computing, Intel, 31 May 2010, <https://www.intel.com/pressroom/archive/releases/2010/20100531comp.htm>

- ↑ a b c Mike Giles (24 June 2010), Runners and riders in GPU steeplechase, pp. 8–10, <http://people.maths.ox.ac.uk/gilesm/talks/nag_tpc10.pdf>

- ↑ a b c d Gareth Halfacree (20 June 2011), Intel pushes for HPC space with Knights Corner, Net Communities Limited, UK, <http://www.thinq.co.uk/2011/6/20/intel-pushes-hpc-space-knights-corner/>

- ↑ Intel Many Integrated Core Architecture, Intel, December 2010, <http://www.many-core.group.cam.ac.uk/ukgpucc2/talks/Elgar.pdf> Archiválva 2012. április 2-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ a b Rick Merritt (20 June 2011), OEMs show systems with Intel MIC chips, <https://www.eetimes.com/electronics-news/4217092/OEMs-show-systems-with-Intel-MIC-chips>

- ↑ Tom R. Halfhill (18 July 2011), Intel Shows MIC Progress, The Linley Group, <http://www.linleygroup.com/newsletters/newsletter_detail.php?num=4729>

- ↑ A „tri-gate” egy térbeli felépítést kihasználó sokkapus tranzisztorok kiépítését lehetővé tevő technológia, amellyel az adott csíkszélesség mellett elérhető tranzisztorszámot növelik.

- ↑ Andrea Petrou (20 June 2011), SGI wants Intel for super supercomputer, <http://news.techeye.net/hardware/sgi-wants-intel-for-super-supercomputer>

- ↑ "Stampede's" Comprehensive Capabilities to Bolster U.S. Open Science Computational Resources, Texas Advanced Computing Center, 22 September 2011, <http://www.tacc.utexas.edu/news/press-releases/2011/stampede> Archiválva 2012. augusztus 5-i dátummal a Wayback Machine-ben

- ↑ a b Stampede: A Comprehensive Petascale Computing Environment. IEEE Cluster 2011 Special Topic. . (Hozzáférés: 2011. november 16.)

- ↑ Faith Singer-Villalobos: STAMPEDE'S KNIGHT'S LANDING EARLY SCIENCE PROGRAM (angol nyelven). TACC, 2015. november 15. (Hozzáférés: 2022. augusztus 5.) „A portion of the Stampede system will be upgraded to the second generation of Xeon Phi™, codenamed "Knight's Landing," in the first half of 2016 in preparation for future systems.”

- ↑ Yam, Marcus (16 November 2011), Intel's Knights Corner: 50+ Core 22nm Co-processor, Tom's Hardware, <https://www.tomshardware.com/news/intel-knights-corner-mic-co-processor,14002.html>. Hozzáférés ideje: 16 November 2011

- ↑ Sylvie Barak (16 November 2011), Intel unveils 1 TFLOP/s Knights Corner, <https://www.eetimes.com/electronics-news/4230654/Intel-unveils-1-TFLOP-s-Knight-s-Corner>. Hozzáférés ideje: 16 November 2011

- ↑ James Reinders (5 June 2012), Knights Corner: Open source software stack, Intel, <https://software.intel.com/en-us/blogs/2012/06/05/knights-corner-open-source-software-stack>

- ↑ Prickett Morgan, Timothy (18 June 2012), Intel slaps Xeon Phi brand on MIC coprocessors, <https://www.theregister.co.uk/2012/06/18/intel_mic_xeon_phi_cray/>

- ↑ Intel Corporation (18 June 2012), Latest Intel Xeon Processors E5 Product Family Achieves Fastest Adoption of New Technology on Top500 List, <http://www.marketwatch.com/story/latest-intelr-xeonr-processors-e5-product-family-achieves-fastest-adoption-of-new-technology-on-top500-list-2012-06-18>. Hozzáférés ideje: 18 June 2012 Archiválva 2012. június 20-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ Raj Hazra. „Intel Xeon Phi coprocessors accelerate the pace of discovery and innovation”, Intel, 2012. június 18. (Hozzáférés: 2012. december 12.)

- ↑ Rick Merritt. „Cray will use Intel MIC, branded Xeon Phi”, EETimes, 2012. június 18. (Hozzáférés: 2012. december 12.)

- ↑ Terrence O'Brien. „Intel christens its 'Many Integrated Core' products Xeon Phi, eyes exascale milestone”, Engadget, 2012. június 18. (Hozzáférés: 2012. december 12.)

- ↑ Jeffrey Burt. „Intel Wraps Xeon Phi Branding Around MIC Coprocessors”, eWeek, 2012. június 18. (Hozzáférés: 2022. március 7.)

- ↑ Merritt, Rick (8 June 2012), Cray will use Intel MIC, branded Xeon Phi, <https://www.eetimes.com/electronics-news/4375500/Cray-will-use-Intel-MIC--branded-Xeon-Phi>

- ↑ Latif, Lawrence (19 June 2012), Cray to support Intel's Xeon Phi in Cascade clusters, <https://www.theinquirer.net/inquirer/news/2184891/cray-support-intels-xeon-phi-cascade-clusters> Archiválva 2012. június 22-i dátummal a Wayback Machine-ben Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ ScaleMP vSMP Foundation to Support Intel Xeon Phi, ScaleMP, 20 June 2012, <http://www.scalemp.com/scalemp-vsmp-foundation-to-support-intel-xeon-phi> Archiválva 2013. május 20-i dátummal a Wayback Machine-ben

- ↑ George Chrysos: Intel Xeon Phi X100 Family Coprocessor - the Architecture. software.intel.com , 2012. november 12.

- ↑ a b c IntelPR. „Intel Delivers New Architecture for Discovery with Intel Xeon Phi Coprocessors”, Intel, 2012. november 12. (Hozzáférés: 2012. december 12.)

- ↑ a b c Agam Shah. Intel ships 60-core Xeon Phi processor [archivált változat] (2012. november 12.). Hozzáférés ideje: 2022. augusztus 5. [archiválás ideje: 2013. március 12.]

- ↑ a b c Johan De Gelas. „The Xeon Phi at work at TACC”, AnandTech, 2012. november 14. (Hozzáférés: 2012. december 12.)

- ↑ Tianhe-2 (MilkyWay-2). Top500.org, 2015. november 14. (Hozzáférés: 2016. május 6.)

- ↑ Intel's 50-core champion: In-depth on Xeon Phi. ExtremeTech. Ziff Davis, Inc., 2012. július 30. (Hozzáférés: 2012. december 2.)

- ↑ (2013) „Manycore Parallelism through OpenMP”. IWOMP 8122: 45–57, Springer. doi:10.1007/978-3-642-40698-0_4.

- ↑ Dokulil, Jiri; Bajrovic, Enes & Benkner, Siegfried et al. (23 November 2012), Efficient Hybrid Execution of C++ Applications using Intel Xeon Phi Coprocessor

- ↑ News Fact Sheet: Intel Many Integrated Core (Intel MIC) Architecture ISC'11 Demos and Performance Description, Intel, 20 June 2011, <https://newsroom.intel.com/servlet/JiveServlet/download/2152-4-5220/ISC_Intel_MIC_factsheet.pdf> Archivált másolat. . (Hozzáférés: 2022. augusztus 5.)

- ↑ Tesla vs. Xeon Phi vs. Radeon. A Compiler Writer’s Perspective // The Portland Group (PGI), CUG 2013 Proceedings

- ↑ Intel Many Integrated Core Architecture (Intel MIC Architecture) - RESOURCES (including downloads). Intel. (Hozzáférés: 2014. január 6.)

- ↑ Intel Xeon Phi Coprocessor Instruction Set Architecture Reference Manual. Intel, 2012. szeptember 7. (Hozzáférés: 2014. január 6.)

- ↑ Intel Developer Zone: Intel Xeon Phi Coprocessor. Intel. (Hozzáférés: 2014. január 6.)

- ↑ Intel® Intrinsics Guide. software.intel.com . (Hozzáférés: 2020. augusztus 4.)

- ↑ a b c dp: dupla pontosságú lebegőpontos

- ↑ Intel SE3110X Xeon Phi 3110X Knights Corner 6GB Coprocessor-No Cooling -SabrePC.com -SabrePC.com (angol nyelven). www.sabrepc.com . . (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 3120A (6GB, 1.100 GHz, 57 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 3120P (6GB, 1.100 GHz, 57 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi 31S1P - BC31S1P. www.cpu-world.com . (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 5110P (8GB, 1.053 GHz, 60 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 5120D (8GB, 1.053 GHz, 60 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi SE10P. www.cpu-world.com . (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi SE10X. www.cpu-world.com . (Hozzáférés: 2017. február 22.)

- ↑ Intel SC7110P Xeon Phi 7110P Knights Corner Coprocessor -SabrePC.com -SabrePC.com (angol nyelven). www.sabrepc.com . (Hozzáférés: 2017. február 22.)

- ↑ Intel SC7110X Xeon Phi 7110X Knights Corner Coprocessor -SabrePC.com -SabrePC.com (angol nyelven). www.sabrepc.com . (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 7120A (16GB, 1.238 GHz, 61 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 7120D (16GB, 1.238 GHz, 61 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 7120P (16GB, 1.238 GHz, 61 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ „Intel Xeon Phi Coprocessor 7120X (16GB, 1.238 GHz, 61 core) Product Specifications”, Intel ARK (Product Specs) (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi 'Knights Landing' Features Integrated Memory With 500 GB/s Bandwidth and DDR4 Memory Support - Architecture Detailed. WCCFtech, 2013. november 25. (Hozzáférés: 2015. augusztus 27.)

- ↑ Sebastian Anthony (26 November 2013), Intel unveils 72-core x86 Knights Landing CPU for exascale supercomputing, ExtremeTech, <https://www.extremetech.com/extreme/171678-intel-unveils-72-core-x86-knights-landing-cpu-for-exascale-supercomputing>

- ↑ Tom's Hardware: Intel Xeon Phi Knights Landing Now Shipping; Omni Path Update, Too. 20 June 2016

- ↑ James Reinders (23 July 2013), AVX-512 Instructions, Intel, <https://software.intel.com/en-us/blogs/2013/avx-512-instructions>

- ↑ Cori. www.nersc.gov . . (Hozzáférés: 2018. november 14.)

- ↑ a b 2016 ISC High Performance: Intel's Rajeeb Hazra Delivers Keynote Address. Vimeo

- ↑ Pradeep Dubey: How Intel Xeon Phi Processors Benefit Machine Learning/Deep Learning Apps and Frameworks. software.intel.com , 2016. június 20.

- ↑ Introducing the Intel Xeon Phi Processor – Your Path to Deeper Insight

- ↑ 48.: 2019. november

- ↑ „Intel Quietly Drops Xeon Phi 7200 Coprocessors”, Phoronix, 2017. augusztus 24. (Hozzáférés: 2017. augusztus 25.)

- ↑ Product Change Notification 116378 - 00. Intel.com . (Hozzáférés: 2018. július 25.)

- ↑ Advanced Vector Extensions

- ↑ Intel Xeon Phi processor: Your Path to Deeper Insight. Intel.com . (Hozzáférés: 2017. február 25.)

- ↑ Intel Xeon Phi Processor 7210 (16GB, 1.30 GHz, 64 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7210F (16GB, 1.30 GHz, 64 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7230 (16GB, 1.30 GHz, 64 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7230F (16GB, 1.30 GHz, 64 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7250 (16GB, 1.40 GHz, 68 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processors. Intel . (Hozzáférés: 2017. február 25.)

- ↑ Intel Xeon Phi Processor 7250F (16GB, 1.40 GHz, 68 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7290 (16GB, 1.50 GHz, 72 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ Intel Xeon Phi Processor 7290F (16GB, 1.50 GHz, 72 core) Product Specifications. Intel ARK (Product Specs). (Hozzáférés: 2017. február 22.)

- ↑ SC14: Supercomputing '14; International Conference for High Performance Computing, Networking, Storage and Analysis in year 2014

- ↑ Eric Gardner (25 November 2014), What public disclosures has Intel made about Knights Landing?, Intel Corporation, <https://software.intel.com/en-us/articles/what-disclosures-has-intel-made-about-knights-landing/>

- ↑ ALCF staff (9 April 2015), Introducing Aurora, <https://www.alcf.anl.gov/articles/introducing-aurora>

- ↑ ALCF staff (9 April 2015), Aurora, <https://aurora.alcf.anl.gov/>

- ↑ „Some Surprises in the 2018 DoE Budget for Supercomputing”, Next Platform, 2017. május 23. (Hozzáférés: 2017. november 13.)

- ↑ „Is Aurora Morphing into an Exascale AI Supercomputer?”, Inside HPC, 2017. június 16. (Hozzáférés: 2017. november 13.)

- ↑ „Unleashing high performance computing today and tomorrow”, Intel IT Peer Network, 2017. november 13.

- ↑ „Intel quietly kills off next-gen Knights Hill Xeon Phi chips”, Tech Report, 2017. november 13. (Hozzáférés: 2017. november 13.)

- ↑ „Intel Announces Knight's Mill: A Xeon Phi for Deep Learning”, Anandtech, 2016. augusztus 17. (Hozzáférés: 2016. augusztus 17.)

- ↑ „Intel Lists Knights Mill Xeon Phi on ARK: Up to 72 cores at 320W with QFMA and VNNI”, Anandtech, 2017. december 19. (Hozzáférés: 2017. december 19.)

- ↑ (2014) „Test-Driving Intel Xeon Phi”. 2014 ACM/SPEC International Conference on Performance Engineering.

- ↑ Memeti, Suejb; Pllana, Sabri & Benkner, Siegfried et al. (29 June 2015), Accelerating DNA Sequence Analysis using Intel Xeon Phi

- ↑ Viebke, Andre; Pllana, Sabri & Benkner, Siegfried et al. (30 June 2015), The Potential of the Intel Xeon Phi for Supervised Deep Learning

- ↑ Jon Stokes: Intel takes wraps off 50-core supercomputing processor plans. Ars Technica , 2011. június 20.

Fordítás

Ez a szócikk részben vagy egészben a Xeon Phi című angol Wikipédia-szócikk ezen változatának fordításán alapul. Az eredeti cikk szerkesztőit annak laptörténete sorolja fel. Ez a jelzés csupán a megfogalmazás eredetét és a szerzői jogokat jelzi, nem szolgál a cikkben szereplő információk forrásmegjelöléseként.

Források

Ld. jegyzetek

További információk

- Intel lapok: Intel Xeon Phi Processors

- Texas Advanced Computing Center – A texasi „Stampede” szuperszámítógép Xeon Phi csipeket tartalmaz. A Stampede maximális teljesítménye elérheti a 10 petaFLOPS-ot.[1]

- ↑ Johan De Gelas. „Intel's Xeon Phi in 10 Petaflops supercomputer”, AnandTech, 2012. szeptember 11. (Hozzáférés: 2012. december 12.)

- Intel Xeon Phi (magyar nyelven) (wiki). HPC. KIFÜ NIIF, 2017. május 9. (Hozzáférés: 2022. augusztus 5.) „Az oldalon található információk segítséget nyújtanak a HPC felhasználóinknak, hogy alkalmazásaikat miként portolhatják valamint optimalizálhatják a hatékonyabb futást szem előtt tartva Intel Xeon Phi koprocesszor kártyákon.” – gyakorlati útmutató, programok fordítása és futtatása Intel Xeon Phi koprocesszor környezetben

- Abu85: Minden Xeon Phi modellt kivégez az Intel (magyar nyelven) (html). Hírek / Processzor / Szerver. prohardver.hu, 2019. május 8. (Hozzáférés: 2022. augusztus 5.) – rövid hír a Xeon Phi sorozat megszüntetéséről